先进封装的工程价值

在半导体制造进入先进工艺边界的当下,“先进封装”正逐步成为系统性能提升的另一条路径。

它并非单纯追求小型化,而是在功耗、带宽、封装面积、系统复杂性等多重约束中,寻求一种工程均衡。从通孔封装到BGA,再到多芯片集成、RDL重分布与中介层桥接,这些演化并非概念驱动,而是以具体问题为起点的技术演进。

本篇文章基于英文电子书《半导体工程师必备的先进封装基础》的1-10页的内容,从带宽与功耗两个核心问题出发,梳理先进封装的基本概念。

Part 1

从互连瓶颈出发:

封装应对带宽与功耗的挑战

现代计算系统已经不再单纯依赖芯片的工艺节点推进来获取性能提升。在片上逻辑愈发复杂、数据吞吐需求持续增长的背景下,数据传输能力正成为新瓶颈。

带宽的提升已不仅取决于芯片内部的I/O能力,更取决于I/O信号如何有效、密集且高速地跨越封装结构进入系统。

所谓“先进封装”,正是针对这一问题提出的结构性解法。

相较于传统边缘引线、引脚焊接结构,它利用更为紧凑的表面贴装形式,如BGA(球栅阵列),在单位面积内集成更多I/O,且布线更短,传输路径更优。

更重要的是,封装内部微互连尺寸远优于印刷电路板的线宽/间距规则,在毫米尺度空间中实现了高密度、多通道的信号传输,大幅度缓解了PCB布线中的瓶颈。

“前沿”(beachfront)是理解封装I/O密度的关键工程概念。芯片的I/O数量与其球栅阵列密度直接相关,但并非所有球都适合用于高速信号传输。

在设计高速总线时,常需考虑信号间匹配、串扰隔离与电气一致性,因此能用于一条并行总线的引脚往往只占总I/O的一部分。

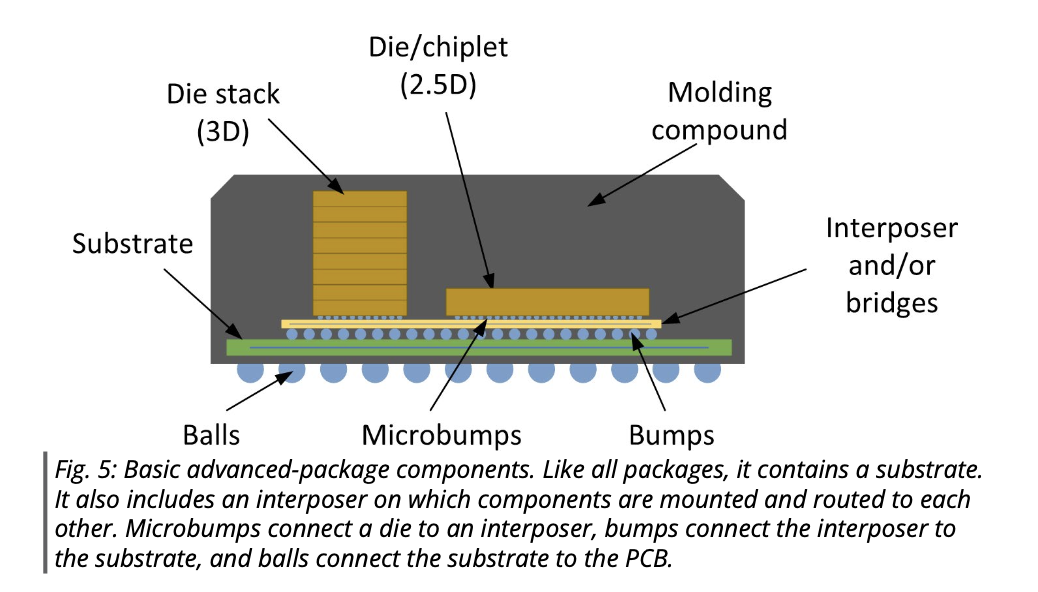

在结构设计上,现代封装通过RDL(重分布层)将密集分布的信号由芯片内核引导至外部接口,使其适应更为宽松的PCB布线规则。以高带宽内存(HBM)为例,其核心优势正是通过封装内部的高密度并行互连实现带宽扩展。

HBM利用2.5D封装方式,将多个内存die通过硅中介层堆叠至主逻辑芯片周围,并通过TSV(硅通孔)及RDL实现互连。相较传统DDR结构,HBM显著缩短了数据通路,降低信号衰减并提升吞吐效率。

而在功耗层面,封装内短距离通信降低了驱动电压与电流需求,从而减小单位bit的传输功耗。这对于移动端、高性能计算(HPC)乃至AI加速芯片尤为关键。在满足性能增长的同时控制总功耗,成为工程设计的一种现实选择。

从工程角度看,这一演进不是凭空创造的新技术,而是对PCB物理极限的回应。当系统I/O数量不断攀升时,封装成为唯一可以在毫米级精度内解决高密度信号传输问题的场域。它承载着“近距离传输 + 多通道并发”的结构使命,是整个系统架构不可忽视的基础支撑。

Part 2

多组件封装与系统集成的工程挑战

与单芯片封装不同,先进封装越来越多地采用多组件集成结构(Multi-Chip Module, MCM),它不再是“封装一个芯片”,而是“在封装中构建一个小型系统”。这类结构的核心技术路径包括2.5D中介层封装、3D堆叠封装以及扇出型封装(FOWLP)等。

2.5D方案通常采用硅中介层,将不同功能的chiplet布置在同一平面,通过微凸点和RDL实现高速互连。这一结构避免了芯片之间通过PCB布线的长路径,显著降低延迟与功耗。该方案在AMD的多核CPU、英伟达GPU、高端FPGA中均已实现量产应用。

而3D堆叠方案则更进一步,将多个裸die垂直叠放,通过TSV进行垂直互联。这种架构可将存储与逻辑紧耦合,形成垂直层级的高速访问路径,但在热设计与良率控制上挑战更大。

3D堆叠对封装内热分布均匀性要求极高,局部热点可能引发性能退化或可靠性下降,因此在移动设备上应用较少,主要出现在高端ASIC和AI加速器芯片中。

封装的复杂性也体现在信号重分布与布局优化上。尤其在高I/O数量的场景下,RDL设计变得愈加关键,它不仅决定了封装的引出路径,还影响着系统的信号完整性与EMI控制。工程上需同时满足:最小路径损耗、最大等长性、最小串扰、最小回环面积等指标。

“扇入”与“扇出”结构的选择也直接影响封装尺寸与系统密度。扇入结构适用于I/O数量较少的芯片,整体封装可紧贴裸die边界,适合移动端小尺寸需求。而扇出结构则为大量I/O的芯片提供更大空间进行信号扩展,是数据中心级芯片与复杂SoC的首选结构。

在集成角度,多芯片封装带来的“连接内移”效应也不容忽视。这一点可从“Rent’s Rule”观察得出:在同一封装内部的两个芯片,其互连不再依赖PCB布线,而是转由封装内实现,带来更高连接效率、更低延迟以及更好的空间利用率。

这种集成也带来了系统性风险。例如,某一个die出现失效可能导致整个封装报废;封装测试覆盖率不足也容易造成早期失效难以及时发现。

此外,可靠性验证难度成倍提升,尤其是中介层与die间的热膨胀系数匹配、键合应力分布、电迁移风险等问题,成为先进封装能否走向量产的关键门槛。

从制造工艺角度看,随着封装内嵌结构不断复杂化,传统分立工艺流程正在向整体协同转变——封装不再是后段工艺的“附加环节”,而是前端架构设计的重要一环。EDA工具的覆盖也必须延伸到封装布局、信号时序仿真、热建模与结构力学等领域,真正做到封装与芯片协同设计。

小结

先进封装的兴起,不仅改变了芯片之间的连接方式,更改变了“系统”本身的结构边界。

从早期封装作为“防护壳”的角色,到如今其成为系统互连、异构协同乃至热管理核心支撑,先进封装正成为半导体系统设计中不可分割的一部分。

当我们无法再通过线性缩小晶体管尺寸来提升系统性能时,工程师的视线自然转向封装,转向互连,转向封装内构建“小型计算系统”的可能。

回归工程实践,先进封装需要工程师真正理解“连接成本”、“封装内功耗”、“路径延迟”与“热耦合”之间的权衡逻辑,这是在多目标约束中寻找局部最优的系统工程工作流。

免责声明:上述内容仅代表发帖人个人观点,不构成本平台的任何投资建议。